## **General Description**

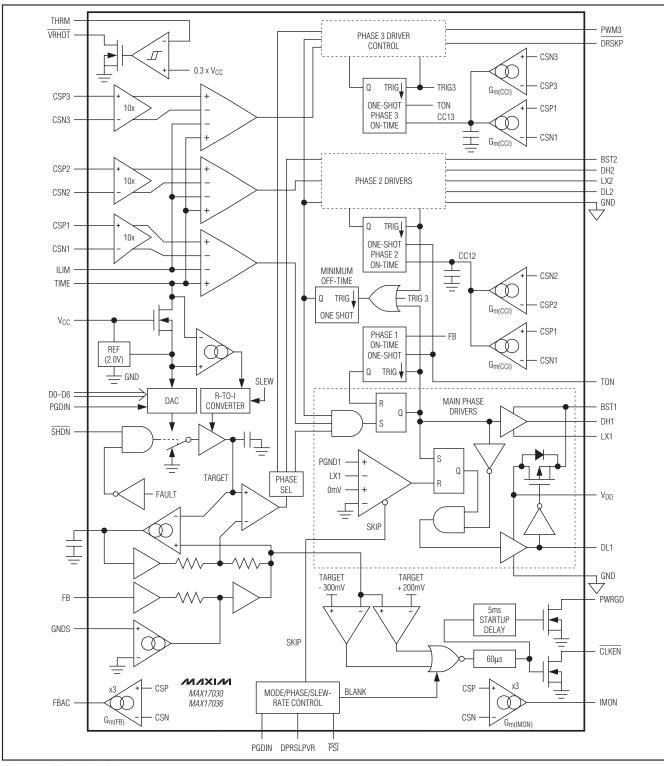

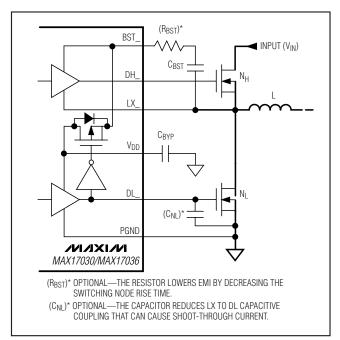

The MAX17030/MAX17036 are 3/2-phase interleaved Quick-PWM<sup>™</sup> step-down VID power-supply controllers for IMVP-6.5 notebook CPUs. Two integrated drivers and the option to drive a third phase using an external driver such as the MAX8791 allow for a flexible 3/2-phase configuration depending on the CPU being supported.

True out-of-phase operation reduces input ripple-current requirements and output-voltage ripple while easing component selection and layout difficulties. The Quick-PWM control provides instantaneous response to fast load-current steps. Active voltage positioning reduces power dissipation and bulk output capacitance requirements and allows ideal positioning compensation for tantalum, polymer, or ceramic bulk output capacitors.

The MAX17030/MAX17036 are intended for bucking down the battery directly to create the core voltage. The single-stage conversion method allows this device to directly step down high-voltage batteries for the highest possible efficiency.

A slew-rate controller allows controlled transitions between VID codes. A thermistor-based temperature sensor provides programmable thermal protection. An output current monitor provides an analog current output proportional to the sum of the inductor currents, which in steady state is the same as the current consumed by the CPU.

## **Applications**

IMVP-6.5 SV and XE Core Power Supplies

High-Current Voltage-Positioned Step-Down Converters

3 to 4 Li+ Cells Battery to CPU Core Supply Converters

Notebooks/Desktops/Servers

| _Ordering In | formation |

|--------------|-----------|

|--------------|-----------|

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX17030GTL+ | -40°C to +105°C | 40 TQFN-EP* |

| MAX17036GTL+ | -40°C to +105°C | 40 TQFN-EP* |

+Denotes a lead-free(Pb)/RoHS-compliant package. \*EP = Exposed pad.

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

##

**\_Features**

- Triple/Dual-Phase Quick-PWM Controllers

- 2 Internal Drivers + 1 External Driver

- ♦ ±0.5% V<sub>OUT</sub> Accuracy Over Line, Load, and Temperature

- ♦ 7-Bit IMVP-6.5 DAC

- Dynamic Phase Selection Optimizes Active/Sleep Efficiency

- Transient Phase Overlap Reduces Output Capacitance

- Transient Suppression Feature (MAX17036 Only)

- Integrated Boost Switches

- Active Voltage Positioning with Adjustable Gain

- Accurate Lossless Current Balance and Current Limit

- Remote Output and Ground Sense

- Adjustable Output Slew-Rate Control

- Power-Good (IMVPOK), Clock Enable (CLKEN), and Thermal-Fault (VRHOT) Outputs

- IMVP-6.5 Power Sequencing and Timing Compliant

- Output Current Monitor (IMON)

- Drives Large Synchronous Rectifier FETs

- ♦ 7V to 26V Battery Input Range

- Adjustable Switching Frequency (600kHz max)

- Undervoltage, Overvoltage, and Thermal-Fault Protection

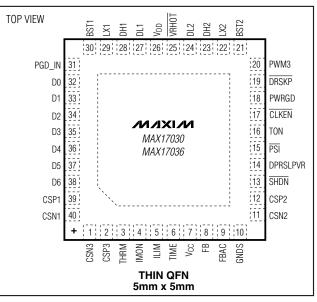

## **Pin Configuration**

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>CC</sub> , V <sub>DD</sub> to GND0.3V to +6V          |

|--------------------------------------------------------------|

| D0–D6, PGD_IN, PSI, DPRSLPVR to GND0.3V to +6V               |

| CSP_, CSN_, THRM, ILIM to GND0.3V to +6V                     |

| PWRGD, CLKEN, VR_HOT to GND0.3V to +6V                       |

| FB, FBAC, IMON, TIME to GND0.3V to (V <sub>CC</sub> + 0.3V)  |

| SHDN to GND (Note 2)0.3V to +30V                             |

| TON to GND0.3V to +30V                                       |

| GNDS to GND0.3V to +0.3V                                     |

| DL1, DL2, PWM3, DRSKP to GND0.3V to (V <sub>DD</sub> + 0.3V) |

| BST1, BST2 to GND0.3V to +36V                                |

| BST1, BST2 to V <sub>DD</sub> 0.3V to +30V                   |

| LX1 to BST1<br>LX2 to BST2<br>DH1 to LX1<br>DH2 to LX2         | -0.3V to (V <sub>BST1</sub> + 0.3V)<br>-0.3V to (V <sub>BST2</sub> + 0.3V) |

|----------------------------------------------------------------|----------------------------------------------------------------------------|

| Continuous Power Dissipation (40-pin, 5<br>Up to +70°C         |                                                                            |

| Derating above +70°C                                           | 22.2mW/°C                                                                  |

| Operating Temperature Range                                    |                                                                            |

| Storage Temperature Range<br>Lead Temperature (soldering, 10s) | 65°C to +165°C                                                             |

Note 1: Absolute Maximum Ratings valid using 20MHz bandwidth limit.

Note 2: SHDN might be forced to 12V for the purpose of debugging prototype breadboards using the no-fault test mode. Internal BST switches are disabled as well. Use external BST diodes when SHDN is forced to 12V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{PGD_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to  $CSN_$ , [D6–D0] = [0101000];  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                  | SYMBOL          | CO                                                                                           | NDITIONS                                                            | MIN   | ТҮР   | МАХ   | UNITS |

|----------------------------|-----------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|

| PWM CONTROLLER             |                 |                                                                                              |                                                                     | •     |       |       |       |

| Input Voltage Pange        |                 | V <sub>CC</sub> , V <sub>DD</sub>                                                            |                                                                     | 4.5   |       | 5.5   | V     |

| Input Voltage Range        |                 | VIN                                                                                          |                                                                     | 7     |       | 26    |       |

| FB Output Voltage Accuracy |                 | Measured at FB<br>with respect to                                                            | DAC codes from<br>0.8125V to 1.5000V                                | -0.5  |       | +0.5  | %     |

|                            | V <sub>FB</sub> | GNDS;<br>includes load-                                                                      | DAC codes from<br>0.3750V to 0.8000V                                | -7    |       | +7    | m)/   |

|                            |                 | regulation error<br>(Note 3)                                                                 | DAC codes from<br>0 to 0.3625V                                      | -20   |       | +20   | mV    |

| Boot Voltage               | VBOOT           |                                                                                              |                                                                     | 1.094 | 1.100 | 1.106 | V     |

| Line Regulation Error      |                 | $V_{CC} = 4.5V$ to 5.5V                                                                      | $V_{CC} = 4.5V$ to 5.5V, $V_{IN} = 4.5V$ to 26V                     |       | 0.1   |       | %     |

| FB Input Bias Current      |                 | $T_A = +25^{\circ}C$                                                                         |                                                                     | -0.1  |       | +0.1  | μA    |

| GNDS Input Range           |                 |                                                                                              |                                                                     | -200  |       | +200  | mV    |

| GNDS Gain                  | AGNDS           | $\Delta V_{OUT}/\Delta V_{GNDS}$                                                             |                                                                     | 0.97  | 1.00  | 1.03  | V/V   |

| GNDS Input Bias Current    | IGNDS           | $T_A = +25^{\circ}C$                                                                         |                                                                     | -0.5  |       | +0.5  | μA    |

| TIME Regulation Voltage    | VTIME           | $R_{TIME} = 147 k\Omega$                                                                     |                                                                     | 1.985 | 2.000 | 2.015 | V     |

|                            |                 | $R_{TIME} = 147 k\Omega (6.$                                                                 | 08mV/µs nominal)                                                    | -10   |       | +10   |       |

| TIME Slew-Rate Accuracy    |                 |                                                                                              | $R_{TIME} = 35.7$ kΩ (25mV/µs nominal) to<br>178kΩ (5mV/µs nominal) |       |       | +15   | %     |

|                            |                 | Soft-start and soft-<br>R <sub>TIME</sub> = $35.7$ k $\Omega$ (6<br>178k $\Omega$ (1.25mV/µs | .25mV/µs nominal) to                                                | -20   |       | +20   |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{PGD_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to  $CSN_$ , [D6–D0] = [0101000]; **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at  $T_A = +25°C$ .)

| PARAMETER                                    | SYMBOL    |                                                                                     | CONDITIONS                                                                                                     | MIN  | ТҮР  | МАХ  | UNITS |

|----------------------------------------------|-----------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                              |           | V <sub>IN</sub> = 10V,<br>V <sub>FB</sub> = 1.0V,                                   | $R_{TON} = 96.75 k\Omega (600 kHz)$ per phase), 167ns nominal                                                  | -15  |      | +15  |       |

| On-Time Accuracy                             | ton       | measured at<br>DH1, DH2,                                                            | $R_{TON} = 200 k\Omega$ (300kHz per phase), 333ns nominal                                                      | -10  |      | +10  | %     |

|                                              |           | and PWM3<br>(Note 4)                                                                | $R_{TON} = 303.25 k\Omega (200 kHz)$<br>per phase), 500ns nominal                                              | -15  |      | +15  |       |

| Minimum Off-Time                             | toff(MIN) | Measured at D                                                                       | H1, DH2, and PWM3 (Note 4)                                                                                     |      | 300  | 375  | ns    |

| TON Shutdown Input Current                   | ITON,SDN  | $\overline{\text{SHDN}} = \text{GND},$<br>or 5V, T <sub>A</sub> = +2                | $V_{IN} = 26V, V_{CC} = V_{DD} = 0$<br>5°C                                                                     |      | 0.01 | 0.1  | μA    |

| BIAS CURRENTS                                |           | •                                                                                   |                                                                                                                |      |      |      |       |

| Quiescent Supply Current (V <sub>CC</sub> )  | ICC       |                                                                                     | CC, VDPRSLPVR = 5V, FB<br>he regulation point                                                                  |      | 3.5  | 7    | mA    |

| Quiescent Supply Current (V <sub>DD</sub> )  | IDD       | Measured at V <sub>E</sub><br>above the regul                                       |                                                                                                                | 0.02 | 1    | μA   |       |

| Shutdown Supply Current (V <sub>CC</sub> )   | ICC,SDN   | Measured at Vo                                                                      | Measured at V <sub>CC</sub> , $\overline{\text{SHDN}}$ = GND, T <sub>A</sub> = +25°C                           |      | 0.01 | 1    | μA    |

| Shutdown Supply Current (V <sub>DD</sub> )   | IDD,SDN   | Measured at $V_{DD}$ , $\overline{SHDN} = GND$ , $T_A = +25^{\circ}C$               |                                                                                                                |      | 0.01 | 1    | μA    |

| FAULT PROTECTION                             |           |                                                                                     |                                                                                                                |      |      |      |       |

| Output Overvoltage-Protection                |           | regulation volt<br>measured at F                                                    | er output reaches the<br>age or PWM mode;<br>B with respect to the voltage<br>ne VID code (see Table 4)        | 250  | 300  | 350  | mV    |

| Threshold                                    | VOVP      | output have no                                                                      | Soft-start, soft-shutdown, skip mode, and<br>output have not reached the regulation<br>voltage; measured at FB |      | 1.50 | 1.55 | V     |

|                                              |           | Minimum OVP                                                                         | threshold; measured at FB                                                                                      |      | 0.8  |      |       |

| Output Overvoltage-<br>Propagation Delay     | tovp      | FB forced 25m                                                                       | FB forced 25mV above trip threshold                                                                            |      | 10   |      | μs    |

| Output Undervoltage-<br>Protection Threshold | Vuvp      | Measured at FB with respect to the voltage target set by the VID code (see Table 4) |                                                                                                                | -450 | -400 | -350 | mV    |

| Output Undervoltage-<br>Propagation Delay    | tuvp      | FB forced 25mV below trip threshold                                                 |                                                                                                                |      | 10   |      | μs    |

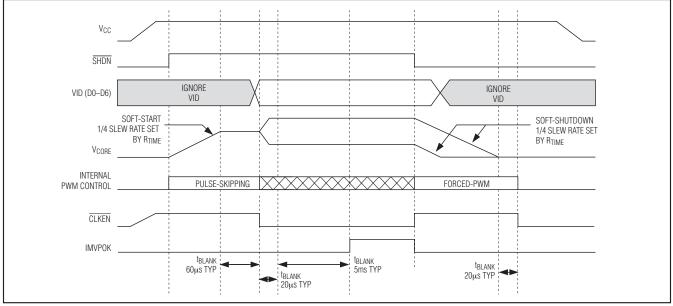

| CLKEN Startup Delay and<br>Boot Time Period  | tвоот     |                                                                                     | n the time when FB reaches<br>voltage (Note 3)                                                                 | 20   | 60   | 100  | μs    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{SHDN} = V_{PGD_IN} = V_{PSI} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to  $CSN_$ , [D6–D0] = [0101000];  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                     | SYMBOL             | CONI                                                                        | DITIONS                                            | MIN  | ТҮР  | MAX  | UNITS |

|---------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------|------|------|------|-------|

| PWRGD Startup Delay                                           |                    | Measured at startup<br>CLKEN goes low                                       | from the time when                                 | 3    | 6.5  | 10   | ms    |

| CLKEN and PWRGD Threshold                                     |                    | Measured at FB<br>with respect to the<br>voltage target set                 | Lower threshold,<br>falling edge<br>(undervoltage) | -350 | -300 | -250 | mV    |

|                                                               |                    | by the VID code<br>(see Table 4), 20mV<br>hysteresis (typ)                  | Upper threshold,<br>rising edge<br>(overvoltage)   | +150 | +200 | +250 |       |

| CLKEN and PWRGD Delay                                         |                    | FB forced 25mV outs thresholds                                              | ide the PWRGD trip                                 |      | 10   |      | μs    |

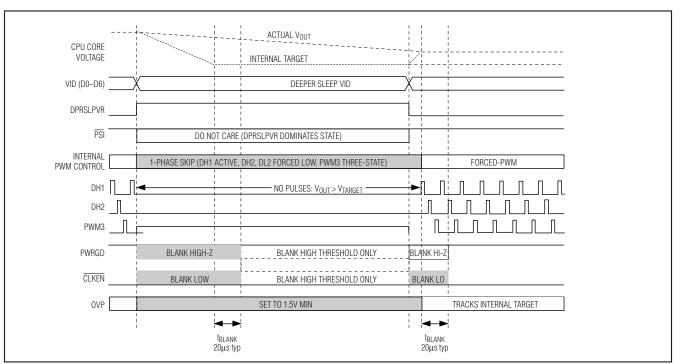

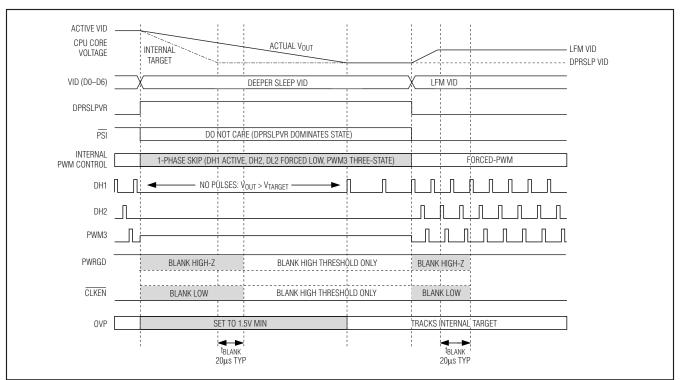

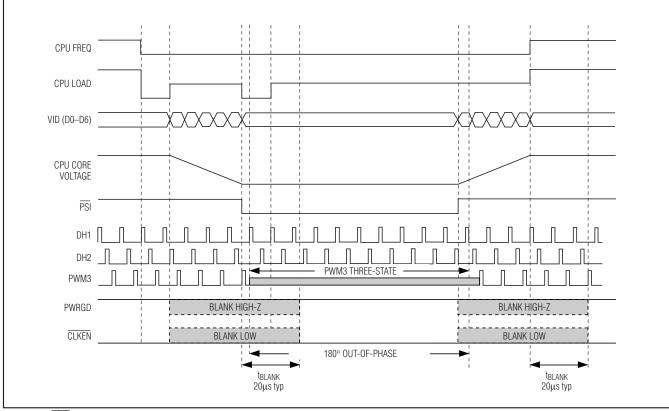

| CLKEN and PWRGD Transition<br>Blanking Time (VID Transitions) | t <sub>BLANK</sub> | Measured from the ti<br>the target voltage (No                              | me when FB reaches<br>ote 3)                       |      | 20   |      | μs    |

| CLKEN, PWRGD Output<br>Low Voltage                            |                    | Low state, I <sub>SINK</sub> = 3r                                           | nA                                                 |      |      | 0.4  | V     |

| CLKEN, PWRGD Leakage<br>Current                               |                    | High-Z state, pin forced to 5V, $T_A = +25^{\circ}C$                        |                                                    |      |      | 1    | μA    |

| CSN1 Pulldown Resistance in<br>UVLO and Shutdown              |                    | SHDN = GND, measured after soft-<br>shutdown completed (DL = low)           |                                                    |      | 8    |      | Ω     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold             | VUVLO(VCC)         | Rising edge, 65mV ty<br>controller disabled b                               |                                                    | 4.05 | 4.27 | 4.48 | V     |

| THERMAL PROTECTION                                            |                    |                                                                             |                                                    |      |      |      |       |

| VRHOT Trip Threshold                                          |                    | Measured at THRM v<br>falling edge, typical                                 |                                                    | 29   | 30   | 31   | %     |

| VRHOT Delay                                                   | t <del>vrhot</del> | THRM forced 25mV to threshold, falling edg                                  |                                                    |      | 10   |      | μs    |

| VRHOT Output On-Resistance                                    | RON(VRHOT)         | Low state                                                                   |                                                    |      | 2    | 8    | Ω     |

| VRHOT Leakage Current                                         |                    | High-Z state, VRHOT 1                                                       | forced to 5V, $T_A = +25^{\circ}C$                 |      |      | 1    | μA    |

| THRM Input Leakage                                            | ITHRM              | $V_{\text{THRM}} = 0$ to 5V, $T_{\text{A}}$ :                               | = +25°C                                            | -0.1 |      | +0.1 | μA    |

| Thermal-Shutdown Threshold                                    | TSHDN              | Typical hysteresis =                                                        | 15°C                                               |      | +160 |      | °C    |

| VALLEY CURRENT LIMIT, DROC                                    | P, CURREN          | F BALANCE, AND CU                                                           | RRENT MONITOR                                      |      |      |      |       |

|                                                               |                    |                                                                             | VTIME - VILIM = 100mV                              | 7    | 10   | 13   |       |

| Current-Limit Threshold Voltage (Positive)                    | VLIMIT             | VCSP VCSN_                                                                  | VTIME - VILIM = 500mV                              | 45   | 50   | 55   | mV    |

|                                                               |                    | Ī                                                                           | $ILIM = V_{CC}$                                    | 20   | 22.5 | 25   |       |

| Current-Limit Threshold Voltage<br>(Negative) Accuracy        | VLIMIT(NEG)        | V <sub>CSP</sub> - V <sub>CSN</sub> , nominally -125% of V <sub>LIMIT</sub> |                                                    | -4   |      | +4   | mV    |

| Current-Limit Threshold Voltage<br>(Zero Crossing)            | Vzx                | V <sub>GND</sub> - V <sub>LX_</sub> , V <sub>DPRSLF</sub>                   | PVR = 5V                                           |      | 0    |      | mV    |

| CSP_, CSN_ Common-Mode<br>Input Range                         |                    |                                                                             |                                                    | 0    |      | 2    | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{PGD_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to  $CSN_$ , [D6–D0] = [0101000]; **TA = 0°C to +85°C**, unless otherwise noted. Typical values are at  $T_A = +25°C$ .)

| PARAMETER                             | SYMBOL               | CON                                                                                                                                                                                         | DITIONS                                     | MIN   | ТҮР                    | MAX                      | UNITS        |

|---------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------|------------------------|--------------------------|--------------|

| Phases 2, 3 Disable Threshold         |                      | Measured at CSP2,                                                                                                                                                                           | CSP3                                        | 3     | V <sub>CC</sub> -<br>1 | V <sub>CC</sub> -<br>0.4 | V            |

| CSP_, CSN_ Input Current              | ICSP, ICSN           | $T_A = +25^{\circ}C$                                                                                                                                                                        |                                             | -0.2  |                        | +0.2                     | μA           |

| ILIM Input Current                    | lilim                | $T_A = +25^{\circ}C$                                                                                                                                                                        |                                             | -0.1  |                        | +0.1                     | μA           |

| Droop Amplifier Offset                |                      | $(1/N) \times \Sigma(V_{CSP} - V_{CSN})$ at IFBAC = 0;<br>$\Sigma$ indicates<br>summation over all                                                                                          | T <sub>A</sub> = +25°C                      | -0.5  |                        | +0.5                     | mV/<br>phase |

|                                       |                      | power-up enabled<br>phases from 1 to N,<br>N = 3                                                                                                                                            | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$ | -0.75 |                        | +0.75                    | -            |

| Droop Amplifier<br>Transconductance   | G <sub>m(FBAC)</sub> | $ \Delta I_{FBAC} / \Delta [\Sigma(V_{CSP} - V_{\Sigma} indicates summate enabled phases from V_{FBAC} = V_{CSN} = 0.4 $                                                                    | 393                                         | 400   | 406                    | μS                       |              |

| Current-Monitor Offset                |                      | $(1/N) \times \Sigma(V_{CSP} - V_{CSP})$<br>$\Sigma$ indicates summate nabled phases from                                                                                                   | -1.1                                        |       | +1                     | mV/<br>phase             |              |

| Current-Monitor<br>Transconductance   | G <sub>m(IMON)</sub> | $ \Delta I_{IMON} / \Delta [\Sigma (V_{CSP} - V_{CSN})]; $ $ \Sigma \text{ indicates summation over all power-up} enabled phases from 1 to N, N = 3, $ $ V_{CSN} = 0.45V \text{ to } 1.5V $ |                                             | 1.552 | 1.6                    | 1.648                    | mS           |

| GATE DRIVERS                          | •                    |                                                                                                                                                                                             |                                             | •     |                        |                          |              |

| DH. Cata Driver On Registeres         | Deview               | BST LX_ forced High state (pullup)                                                                                                                                                          |                                             |       | 0.9                    | 2.5                      | 0            |

| DH_Gate-Driver On-Resistance          | R <sub>ON(DH)</sub>  | to 5V                                                                                                                                                                                       | Low state (pulldown)                        |       | 0.7                    | 2                        | Ω            |

| DI Cata Driver On Registeres          | Power                |                                                                                                                                                                                             | High state (pullup)                         |       | 0.7                    | 2                        | Ω            |

| DL_Gate-Driver On-Resistance          | RON(DL)              |                                                                                                                                                                                             | Low state (pulldown)                        |       | 0.25                   | 0.7                      | 52           |

| DH_ Gate-Driver Source Current        | IDH(SOURCE)          | DH_ forced to 2.5V,<br>BST LX_ forced to                                                                                                                                                    | 5 5 V                                       |       | 2.2                    |                          | А            |

| DH_Gate-Driver Sink Current           | IDH(SINK)            | DH_ forced to 2.5V,<br>BST LX_ forced to                                                                                                                                                    | o 5V                                        |       | 2.7                    |                          | А            |

| DL_ Gate-Driver Source Current        | IDL(SOURCE)          | DL_ forced to 2.5V                                                                                                                                                                          |                                             |       | 2.7                    |                          | А            |

| DL_ Gate-Driver Sink Current          | IDL(SINK)            | DL_ forced to 2.5V                                                                                                                                                                          |                                             |       | 8                      |                          | А            |

| DL_ Transition Time                   |                      | DL_ falling, C <sub>DL_</sub> =                                                                                                                                                             | 3nF                                         |       | 20                     |                          | <b>n</b> 0   |

| DL rising, C <sub>DL</sub> = 3nF      |                      |                                                                                                                                                                                             | 20                                          |       | ns                     |                          |              |

| DH_ Transition Time                   |                      | DH_ falling, C <sub>DH</sub> _ =                                                                                                                                                            | 3nF                                         |       | 20                     |                          | ns           |

|                                       |                      | $DH_rising, C_{DH_} =$                                                                                                                                                                      | 3nF                                         |       | 20                     |                          | 113          |

| Internal BST_ Switch<br>On-Resistance | R <sub>ON(BST)</sub> | I <sub>BST_</sub> = 10mA                                                                                                                                                                    |                                             |       | 10                     | 20                       | Ω            |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{SHDN} = V_{PGD_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to  $CSN_$ , [D6–D0] = [0101000];  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                               | SYMBOL | CONDITIONS                                                                               |                           | ТҮР | MAX  | UNITS |

|-----------------------------------------|--------|------------------------------------------------------------------------------------------|---------------------------|-----|------|-------|

| PWM3, DRSKP OUTPUTS                     | -      |                                                                                          | •                         |     |      |       |

| PWM3, DRSKP Output<br>High Voltages     |        | ISOURCE = 3mA                                                                            | V <sub>DD</sub> -<br>0.4V |     |      | V     |

| PWM3, DRSKP Output<br>Low Voltages      |        | I <sub>SINK</sub> = 3mA                                                                  |                           |     | 0.4  | V     |

| LOGIC AND I/O                           |        | •                                                                                        |                           |     |      |       |

| Logic-Input High Voltage                | VIH    | SHDN, PGD_IN                                                                             | 2.3                       |     |      | V     |

| Logic-Input Low Voltage                 | VIL    | SHDN, PGD_IN                                                                             |                           |     | 1.0  | V     |

| Low-Voltage Logic-Input<br>High Voltage | VIHLV  | PSI, D0–D6, DPRSLPVR                                                                     | 0.67                      |     |      | V     |

| Low-Voltage Logic-Input<br>Low Voltage  | VILLV  | PSI, D0–D6, DPRSLPVR                                                                     |                           |     | 0.33 | V     |

| Logic Input Current                     |        | $T_A = +25^{\circ}C; \overline{SHDN}, DPRSLPVR, PGD_IN, \overline{PSI}, D0-D6 = 0 or 5V$ | -1                        |     | +1   | μA    |

## **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{PGD\_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP\_} = V_{CSN\_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to  $CSN\_$ , [D6-D0] = [0101000];  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted.) (Note 5)

| PARAMETER                  | SYMBOL          |                                                                                                                                | CONDITIONS                           | MIN   | ТҮР | МАХ   | UNITS |

|----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|-----|-------|-------|

| PWM CONTROLLER             | - 1             | 1                                                                                                                              |                                      | •     |     |       |       |

| Input Voltage Range        |                 | V <sub>CC</sub> , V <sub>DD</sub>                                                                                              |                                      | 4.5   |     | 5.5   | V     |

| input voltage hange        |                 | VIN                                                                                                                            |                                      | 7     |     | 26    | v     |

| FB Output-Voltage Accuracy |                 | Measured at<br>FB with                                                                                                         | DAC codes from<br>0.8125V to 1.5000V | -0.75 |     | +0.75 | %     |

|                            | V <sub>FB</sub> | respect to<br>GNDS,<br>includes load-                                                                                          | DAC codes from<br>0.3750V to 0.8000V | -10   |     | +10   | mV    |

|                            |                 | regulation<br>error (Note 3)                                                                                                   | DAC codes from<br>0 to 0.3625V       | -25   |     | +25   |       |

| Boot Voltage               | VBOOT           |                                                                                                                                |                                      | 1.085 |     | 1.115 | V     |

| GNDS Input Range           |                 |                                                                                                                                |                                      | -200  |     | +200  | mV    |

| GNDS Gain                  | AGNDS           | $\Delta V_{OUT} / \Delta V_{GNDS}$                                                                                             |                                      | 0.95  |     | 1.05  | V/V   |

| TIME Regulation Voltage    | VTIME           | $R_{TIME} = 147 k\Omega$                                                                                                       | 1                                    | 1.985 |     | 2.015 | V     |

|                            |                 | $R_{TIME} = 147 k\Omega$                                                                                                       | e (6.08mV/µs nominal)                | -10   |     | +10   |       |

| TIME Slew-Rate Accuracy    |                 | $R_{\text{TIME}} = 35.7 \text{k}\Omega$ $178 \text{k}\Omega (5 \text{mV/}\mu\text{s})$                                         | 2 (25mV/µs nominal) to<br>5 nominal) | -15   |     | +15   | %     |

|                            |                 | Soft-start and soft-shutdown:<br>$R_{TIME} = 35.7 k\Omega (6.25 mV/\mu s nominal) to$<br>$178 k\Omega (1.25 mV/\mu s nominal)$ |                                      | -20   |     | +20   | ,0    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{PGD_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to CSN\_, [D6-D0] = [0101000]; **T<sub>A</sub> = -40°C to +105°C**, unless otherwise noted.) (Note 5)

| PARAMETER                                         | SYMBOL            |                                                                                     | CONDITIONS                                                                                                     | MIN    | ТҮР                                | MAX  | UNITS |      |   |

|---------------------------------------------------|-------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|------------------------------------|------|-------|------|---|

|                                                   |                   | V <sub>IN</sub> = 10V,<br>V <sub>FB</sub> = 1.0V,                                   | $R_{TON} = 96.75 k\Omega (600 kHz per phase), 167 ns nomina$                                                   | .l -15 |                                    | +15  |       |      |   |

| On-Time Accuracy                                  | ton               | measured at<br>DH1, DH2,                                                            | $R_{TON} = 200 k\Omega$ (300kHz per phase), 333ns nomina                                                       | 10     |                                    | +10  | %     |      |   |

|                                                   |                   | and PWM3<br>(Note 4)                                                                | $R_{TON} = 303.25 k\Omega (200 kH per phase), 500 ns nomina$                                                   | 1 -15  |                                    | +15  |       |      |   |

| Minimum Off-Time                                  | toff(MIN)         | Measured at DH                                                                      | 1, DH2, and PWM3 (Note 4)                                                                                      |        |                                    | 400  | ns    |      |   |

| BIAS CURRENTS                                     |                   |                                                                                     |                                                                                                                |        |                                    |      |       |      |   |

| Quiescent Supply Current (V <sub>CC</sub> )       | Icc               |                                                                                     | C, DPRSLPVR = 5V, FB<br>e regulation point                                                                     |        |                                    | 7    | mA    |      |   |

| FAULT PROTECTION                                  |                   |                                                                                     |                                                                                                                |        |                                    |      |       |      |   |

| Output Overvoltage-Protection<br>Threshold        | V <sub>OVP</sub>  | regulation volta<br>measured at FB                                                  | output reaches the<br>ge or PWM mode;<br>with respect to the voltag<br>VID code (see Table 4)                  | e 250  |                                    | 350  | mV    |      |   |

| Theshold                                          |                   | output have not                                                                     | Soft-start, soft-shutdown, skip mode, and<br>output have not reached the regulation<br>voltage; measured at FB |        | ave not reached the regulation 1.4 |      |       | 1.55 | V |

| Output Undervoltage-Protection<br>Threshold       | VUVP              | Measured at FB with respect to the voltage target set by the VID code (see Table 4) |                                                                                                                | e -450 |                                    | -350 | mV    |      |   |

| CLKEN Startup Delay and Boot<br>Time Period       | <sup>t</sup> BOOT | Measured from the boot target v                                                     | the time when FB reaches<br>/oltage (Note 3)                                                                   | 20     |                                    | 100  | μs    |      |   |

| PWRGD Startup Delay                               |                   | Measured at sta<br>CLKEN goes lov                                                   | artup from the time when<br>w                                                                                  | 3      |                                    | 10   | ms    |      |   |

|                                                   |                   | Measured at FB<br>with respect to th<br>voltage target se                           | falling edge                                                                                                   | -350   |                                    | -250 |       |      |   |

| CLKEN and PWRGD Threshold                         |                   | by the VID code<br>(see Table 4),<br>20mV hysteresis<br>(typ)                       | Upper threshold,<br>rising edge<br>(overvoltage)                                                               | +150   |                                    | +250 | mV    |      |   |

| CLKEN, PWRGD Output<br>Low Voltage                |                   | Low state, I <sub>SINK</sub> = 3mA                                                  |                                                                                                                |        |                                    | 0.4  | V     |      |   |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold | VUVLO(VCC)        | Rising edge, 65mV typical hysteresis, controller disabled below this level          |                                                                                                                | 4.05   |                                    | 4.5  | V     |      |   |

| THERMAL PROTECTION                                | ·                 | ·                                                                                   |                                                                                                                |        |                                    |      |       |      |   |

| VRHOT Trip Threshold                              |                   |                                                                                     | IRM with respect to V <sub>CC</sub> ,<br>pical hysteresis = 75mV                                               | 29     |                                    | 31   | %     |      |   |

| VRHOT Output On-Resistance                        | RON(VRHOT)        | Low state                                                                           |                                                                                                                |        |                                    | 8    | Ω     |      |   |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 10V$ ,  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{PGD_IN} = V_{\overline{PSI}} = V_{ILIM} = 5V$ ,  $V_{DPRSLPVR} = V_{GNDS} = 0$ ,  $V_{CSP_} = V_{CSN_} = 1.0000V$ , FB = FBAC,  $R_{FBAC} = 3.57k\Omega$  from FBAC to CSN\_, [D6-D0] = [0101000];  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted.) (Note 5)

| PARAMETER                                              | SYMBOL               | C                                                                                                                                                                                                  | ONDITIONS                                                                                      | MIN                       | ТҮР | MAX                      | UNITS        |

|--------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------|-----|--------------------------|--------------|

| VALLEY CURRENT LIMIT, DROC                             | P, CURREN            | F BALANCE, AND                                                                                                                                                                                     | CURRENT MONITOR                                                                                |                           |     |                          |              |

|                                                        | P                    |                                                                                                                                                                                                    | VTIME - VILIM = 100mV                                                                          | 7                         |     | 13                       |              |

| Current-Limit Threshold Voltage (Positive)             | VLIMIT               | V <sub>CSP</sub> V <sub>CSN</sub> _                                                                                                                                                                | VTIME - VILIM = 500mV                                                                          | 45                        |     | 55                       | mV           |

| (1031110)                                              |                      |                                                                                                                                                                                                    | $ILIM = V_{CC}$                                                                                | 20                        |     | 25                       |              |

| Current-Limit Threshold Voltage<br>(Negative) Accuracy | VLIMIT(NEG)          | V <sub>CSP</sub> V <sub>CSN</sub> _, no                                                                                                                                                            | pminally -125% of $V_{LIMIT}$                                                                  | -4                        |     | +4                       | mV           |

| CSP_, CSN_ Common-Mode<br>Input Range                  |                      |                                                                                                                                                                                                    |                                                                                                | 0                         |     | 2                        | V            |

| Phases 2, 3 Disable Threshold                          |                      | Measured at CSP                                                                                                                                                                                    | 2, CSP3                                                                                        | 3                         |     | V <sub>CC</sub> -<br>0.4 | V            |

| Droop Amplifier Offset                                 |                      | $\Sigma$ indicates summ                                                                                                                                                                            | V <sub>CSN</sub> ) at I <sub>FBAC</sub> = 0;<br>nation over all power-up<br>from 1 to N, N = 3 | -1                        |     | +1                       | mV/<br>phase |

| Droop Amplifier<br>Transconductance                    | G <sub>m(FBAC)</sub> | $\Delta I_{FBAC}/\Delta[\Sigma(V_{CSP} - V_{CSN})]; \Sigma \text{ indicates}$<br>summation over all power-up enabled<br>phases from 1 to N, N = 3,<br>V_{FBAC} = V_{CSN} = 0.45V to 1.5V           |                                                                                                | 390                       |     | 407                      | μS           |

| Current-Monitor Offset                                 |                      | $(1/N) \times \Sigma(V_{CSP} - V_{CSN})$ at I <sub>FBAC</sub> = 0;<br>$\Sigma$ indicates summation over all power-up<br>enabled phases from 1 to N, N = 3                                          |                                                                                                | -1.5                      |     | +1.5                     | mV/<br>phase |

| Current-Monitor<br>Transconductance                    | G <sub>m(IMON)</sub> | $ \frac{\Delta I_{IMON} \Delta [\Sigma (V_{CSP} - V_{CSN})]; \Sigma \text{ indicates} }{\text{summation over all power-up enabled phases} } $ from 1 to N, N = 3, V <sub>CSN</sub> = 0.45V to 1.5V |                                                                                                | 1.536                     |     | 1.664                    | mS           |

| GATE DRIVERS                                           |                      | •                                                                                                                                                                                                  |                                                                                                |                           |     |                          |              |

| DH_ Gate-Driver On-Resistance                          | Bonkous              | BST_ – LX_                                                                                                                                                                                         | High state (pullup)                                                                            |                           |     | 2.5                      | Ω            |

| Dri_ Gale-Driver Orrinesistance                        | R <sub>ON</sub> (DH) | forced to 5V                                                                                                                                                                                       | Low state (pulldown)                                                                           |                           |     | 2                        | 52           |

| DL_ Gate-Driver On-Resistance                          | BONIDIA              | High state (pullur                                                                                                                                                                                 | o)                                                                                             |                           |     | 2                        | Ω            |

|                                                        | R <sub>ON(DL)</sub>  | Low state (pulldo                                                                                                                                                                                  | wn)                                                                                            |                           |     | 0.7                      | 32           |

| Internal BST_ Switch<br>On-Resistance                  | R <sub>ON(BST)</sub> | I <sub>BST-</sub> = 10mA                                                                                                                                                                           |                                                                                                |                           |     | 20                       | Ω            |

| PWM3, DRSKP OUTPUTS                                    |                      |                                                                                                                                                                                                    |                                                                                                |                           |     |                          |              |

| PWM3, DRSKP Output<br>High Voltages                    |                      | ISOURCE = 3mA                                                                                                                                                                                      |                                                                                                | V <sub>DD</sub> -<br>0.4V |     |                          | V            |

| PWM3, DRSKP Output<br>Low Voltages                     |                      | I <sub>SINK</sub> = 3mA                                                                                                                                                                            |                                                                                                |                           |     | 0.4                      | V            |

| LOGIC AND I/O                                          | 1                    |                                                                                                                                                                                                    |                                                                                                |                           |     |                          |              |

| Logic-Input High Voltage                               | VIH                  | SHDN, PGD_IN                                                                                                                                                                                       |                                                                                                | 2.3                       |     |                          | V            |

| Logic-Input Low Voltage                                | VIL                  | SHDN, PGD_IN                                                                                                                                                                                       |                                                                                                |                           |     | 1.0                      | V            |

| Low-Voltage Logic-Input<br>High Voltage                | VIHLV                | PSI, D0–D6, DPR                                                                                                                                                                                    | SLPVR                                                                                          | 0.67                      |     |                          | V            |

| Low-Voltage Logic-Input<br>Low Voltage                 | VILLV                | PSI, D0–D6, DPR                                                                                                                                                                                    | SLPVR                                                                                          |                           |     | 0.33                     | V            |

M/IXI/M

# MAX17030/MAX17036

# 1/2/3-Phase Quick-PWM IMVP-6.5 VID Controllers

## **ELECTRICAL CHARACTERISTICS (continued)**

Note 3: The equation for the target voltage VTARGET is:

$V_{TARGET}$  = The slew-rate-controlled version of  $V_{DAC}$ , where  $V_{DAC}$  = 0 for shutdown

$V_{DAC} = V_{BOOT}$  during IMVP-6.5 startup

V<sub>DAC</sub> = V<sub>VID</sub> otherwise (the V<sub>VID</sub> voltages for all possible VID codes are given in Table 4).

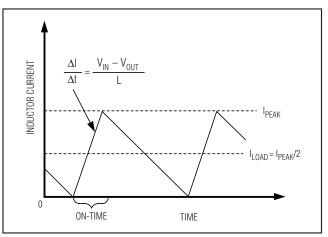

- In pulse-skipping mode, the output rises by approximately 1.5% when transitioning from continuous conduction to no load. **Note 4:** On-time and minimum off-time specifications are measured from 50% to 50% at the DH\_ pin, with LX\_ forced to 0V, BST\_

- forced to 5V, and a 500pF capacitor from DH\_ to LX\_ to simulate external MOSFET gate capacitance. Actual in-circuit times might be different due to MOSFET switching speeds.

Note 5: Specifications to -40°C and +105°C are guaranteed by design, not production tested.

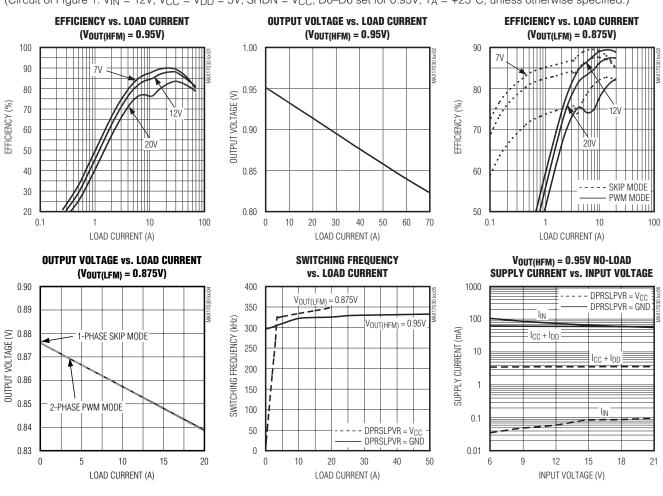

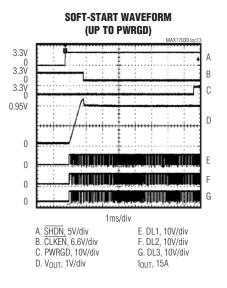

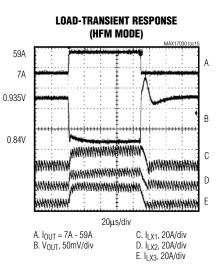

## **Typical Operating Characteristics**

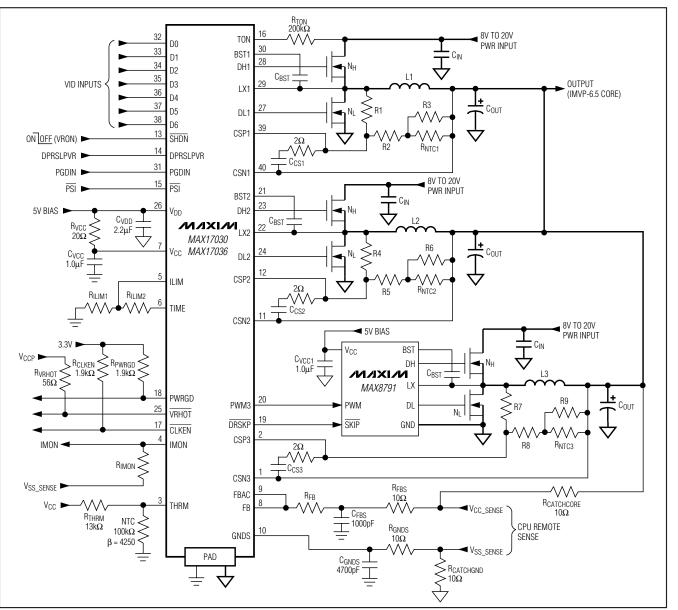

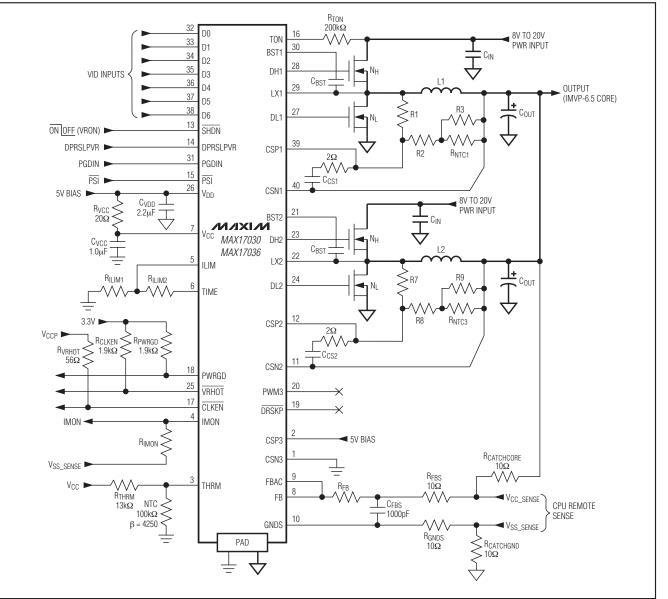

(Circuit of Figure 1. VIN = 12V, VCC = VDD = 5V, SHDN = VCC, D0-D6 set for 0.95V, TA = +25°C, unless otherwise specified.)

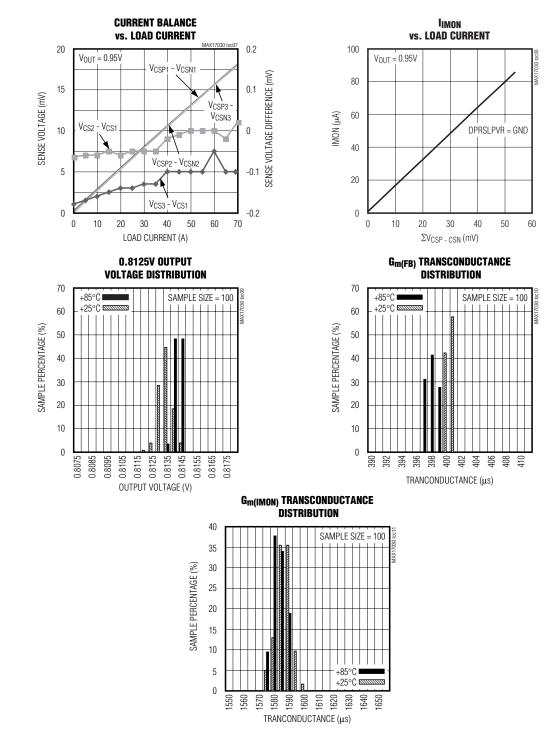

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD} = 5V$ ,  $\overline{SHDN} = V_{CC}$ , D0–D6 set for 0.95V,  $T_A = +25^{\circ}C$ , unless otherwise specified.)

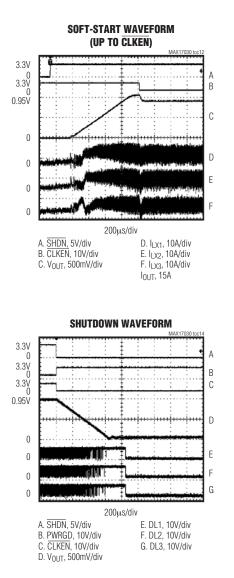

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $V_{CC}$  =  $V_{DD}$  = 5V,  $\overline{SHDN}$  =  $V_{CC}$ , D0–D6 set for 0.95V,  $T_A$  = +25°C, unless otherwise specified.)

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

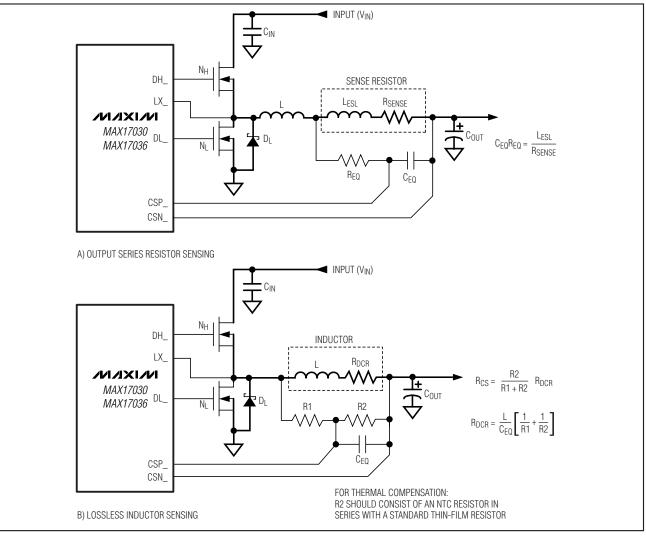

| 1   | CSN3 | Negative Input of the Output Current Sense of Phase 3. This pin should be connected to the negative side of the output current-sensing resistor or the filtering capacitor if the DC resistance of the output inductor is utilized for current sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | CSP3 | Positive Input of the Output Current Sense of Phase 3. This pin should be connected to the positive side of the output current-sensing resistor or the filtering capacitor if the DC resistance of the output inductor is utilized for current sensing.<br>To disable phase 3, connect CSP3 to V <sub>CC</sub> and CSN3 to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3   | THRM | Input of Internal Comparator. Connect the output of a resistor- and thermistor-divider (between $V_{CC}$ and GND) to THRM. Select the components such that the voltage at THRM falls below 1.5V (30% of $V_{CC}$ ) at the desired high temperature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | IMON | Current Monitor Output Pin. The output current at this pin is:<br>$I_{IMON} = G_{M(IMON)} \times \Sigma V(CSP\_,CSN\_)$ where G <sub>M(IMON)</sub> = 1.6mS typical and $\Sigma$ denotes summation over all enabled phases.<br>An external resistor R <sub>IMON</sub> between IMON and GNDS sets the current-monitor output voltage:<br>$V_{IMON} = I_{LOAD} \times R_{SENSE} \times G_{M(IMON)} \times R_{IMON}$ where R <sub>SENSE</sub> is the value of the effective current-sense resistance.<br>Choose R <sub>IMON</sub> such that V <sub>IMON</sub> does not exceed 900mV at the maximum expected load current I <sub>MAX</sub> .<br>IMON is high impedance when the MAX17030/MAX17036 are in shutdown.                                                                        |

| 5   | ILIM | Current-Limit Adjust Input. The valley positive current-limit threshold voltages at V(CSP_,CSN_) are precisely 1/10 the differential voltage V(TIME,ILIM) over a 0.1V to 0.5V range of V(TIME,ILIM). The valley negative current-limit thresholds are typically -125% of the corresponding valley positive current-limit thresholds. Connect ILIM to V <sub>CC</sub> to get the default current-limit threshold setting of 22.5mV typ.                                                                                                                                                                                                                                                                                                                                               |

| 6   | TIME | Slew-Rate Adjustment Pin. The total resistance $R_{TIME}$ from TIME to GND sets the internal slew rate:<br>Slew rate = (12.5mV/µs) x (71.5kΩ/R <sub>TIME</sub> )<br>where $R_{TIME}$ is between 35.7kΩ and 178kΩ.<br>This "normal" slew rate applies to transitions into and out of the low-power pulse-skipping modes<br>and to the transition from boot mode to VID. The slew rate for startup and for entering shutdown is<br>always 1/4 of normal. If the VID DAC inputs are clocked, the slew rate for all other VID transitions<br>is set by the rate at which they are clocked, up to a maximum slew rate equal to the normal slew<br>rate defined above.                                                                                                                     |

| 7   | Vcc  | Controller Supply Voltage. Connect to a 4.5V to 5.5V source. Bypass to GND with 1µF minimum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8   | FB   | Feedback Voltage Input. The voltage at the FB pin is compared with the slew-rate-controlled target voltage by the error comparator (fast regulation loop), as well as by the internal voltage integrator (slow, accurate regulation loop). Having sufficient ripple signal at FB that is in phase with the sum of the inductor currents is essential for cycle-by-cycle stability. The external connections and compensation at FB depend on the desired DC and transient (AC) droop values. If DC droop = AC droop, then short FB to FBAC. To disable DC droop, connect FB to the remote-sensed output voltage through a resistor R and feed forward the FBAC ripple to FB through capacitor C, where the R x C time constant should be at least 3x the switching period per phase. |

## Pin Description (continued)

| PIN | NAME     |                                                                                                                                                                                                                                                                                                                                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 9   | FBAC     | FBAC and the positive<br>the stability, load-tran<br>where R <sub>DROOP,AC</sub> is t<br>tradeoff between stab                                                                                                                                                                                                                  | Positioning Transconductance Amplifier. Connect a resistor R <sub>FBAC</sub> between<br>e side of the feedback remote sense to set the transient (AC) droop based on<br>sient response, and voltage-positioning gain requirements:<br>R <sub>FBAC</sub> = R <sub>DROOP,AC</sub> /[R <sub>SENSE</sub> × G <sub>m</sub> (FBAC)]<br>he transient (AC) voltage-positioning slope that provides an acceptable<br>lity and load-transient response, G <sub>m</sub> (FBAC) = 400µS typ, and R <sub>SENSE</sub> is the<br>e resistance that is used to provide the (CSP_, CSN_) current-sense voltages.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|     |          | used, then the minimu<br>ESR of the output capa<br>If lossless sensing (ir                                                                                                                                                                                                                                                      | nductor DCR sensing) is used, use a thermistor-resistor network to minimize ndence of the voltage-positioning slope.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 10  | GNDS     | GNDS internally conne                                                                                                                                                                                                                                                                                                           | nse Input, Negative Side. Normally connected to GND directly at the load.<br>ects to a transconductance amplifier that fine tunes the output voltage<br>age drops from the regulator ground to the load ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 11  | CSN2     | negative side of the o                                                                                                                                                                                                                                                                                                          | Negative Input of the Output Current Sense of Phase 2. This pin should be connected to the negative side of the output current-sensing resistor or the filtering capacitor if the DC resistance of the output inductor is utilized for current sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

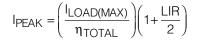

| 12  | CSP2     | Positive Input of the Output Current Sense of Phase 2. This pin should be connected to the positive side of the output current-sensing resistor or the filtering capacitor if the DC resistance of the output inductor is utilized for current sensing.<br>To disable phase 2, connect CSP2 to V <sub>CC</sub> and CSN2 to GND. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |